片上系统概述

片上系统设计简介

Xilinx Unified Software Platform(联合软件开发平台)是一个新的工具,它将赛灵思软件开发的所有软件整合到一个统一的环境。您可以在以下链接上找到大量文档:

Xilinx最初为软件开发而推出的SDx Environments,其中包含:

- SDSoc:用于Zynq UltraScale + MPSoC和Zynq-7000 SoC系列嵌入软件开发

- SDAccel:用于基于数据中心和PCIe的加速器系统软件开发

Vitis 联合软件开发平台将这些流程,以及Xilinx SDK合并在一个环境中,而SDx不再进行更新。因此,Xilinx推荐Vitis进行未来的新开发,这是我们为该课程选择的工具(特别是Vitis Core Development Kit-2019.2)。

开发系统安装

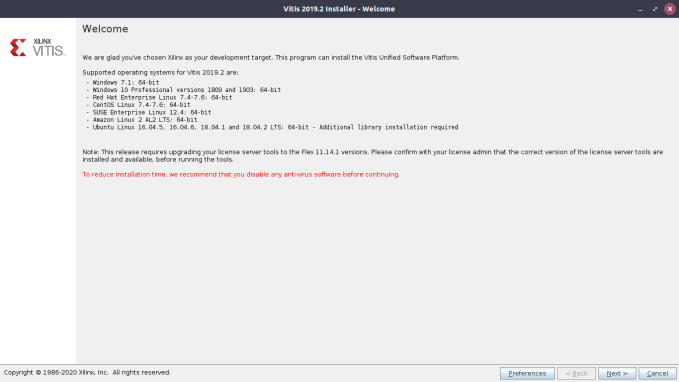

为了方便大多数使用Windows操作系统的人员学习,在本课程中,我们将使用Linux虚拟机,请先参照此步骤安装虚拟机。虚拟机安装完毕后,您可以从Xilinx Vitis下载站点下载Vitis核心开发套件-2019.2。 此处强调:Vitis已在安装中包括Vivado,因此您无需将其作为单独的工具进行安装。Xilinx统一安装程序2019.2为Linux自解压Web安装程序,点击下载,下载前需要注册Xilinx账号。自解压文件大小为115.4 MB,它会在安装时下载所选组件。

在获得一个可以与bash一起安装的二进制文件后,可选择将工具链安装在Linux用户的文件夹中,请运行以下命令(此处$为Linux提示符):

$ bash Downloads/Xilinx_Unified_2019.2_1106_2127_Lin64.bin

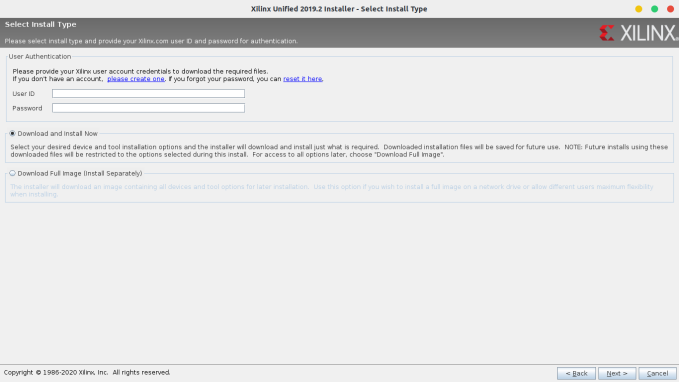

此时,您需要输入Xilinx用户名和密码(如下图),以下载组件。

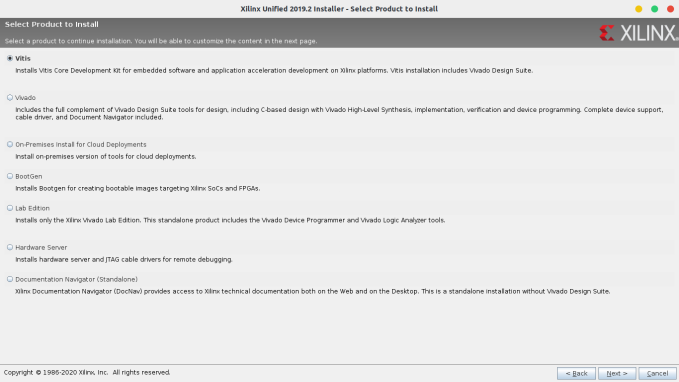

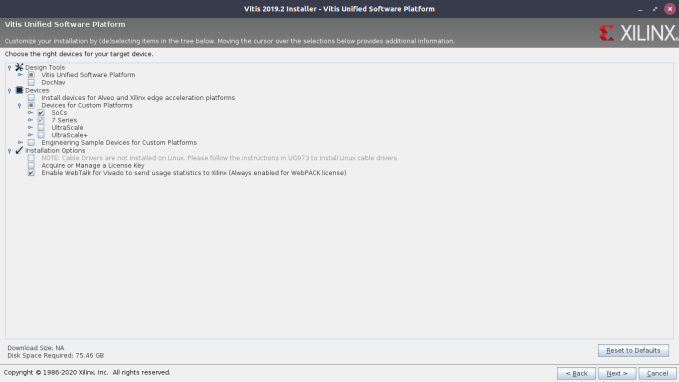

完成后,将要求您选择要安装的组件。在这种情况下,我们将选择Vitis安装完整的Vitis Core Development Kit , 请注意,这还会下载并安装所需的Xilinx Vivado版本。

硬件要求

我们还需要满足一些硬件要求才能完成所有内容。与标准Zynq UltraScale + MPSoC配合使用的最小设置需要多达76GB的可用磁盘空间(完整安装需要90GB)。

此外,如果打算使用Vivado构建自己的PL设计,则需要一台具有大量可用RAM内存的机器。您可以点此检查每台FPGA开发板设备所需的Vivado内存推荐。

由于本课程采用基于XCZU3EG FPGA的Avnet Ultra96v2板,因此Vivado需要4GB典型RAM和6GB峰值RAM,一般计算机均可满足。

许可证

如果您使用Zynq 7000系列,Ultra96V2开发板或ZCU04开发板载FPGA器件,则不需要许可证。为了使用更大容量的FPGA器件,则需要安装Vivado的全功能许可证。

当使用较小的器件(例如Avnet Ultra96v2中的XCZU3EG)时,您不需要向Xilinx申请任何许可证,因为Vitis和Vivado已经包括了现成的集成Webpack许可证,供直接使用。

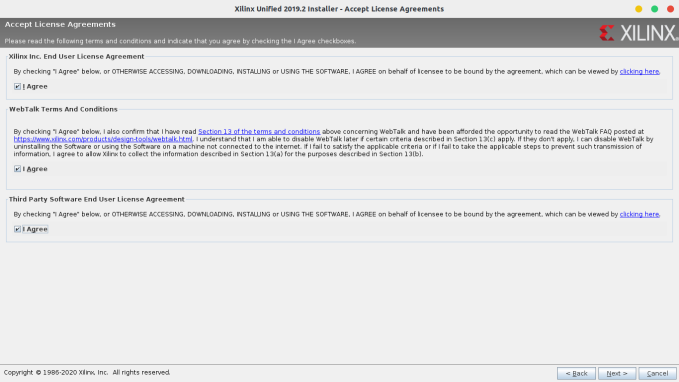

点此,可以查看Webpack免费许可证支持的设备的完整列表。如果您打算使用此Webpack许可证,则必须在安装时或以后启用Xilinx Webtalk,如下图所示。